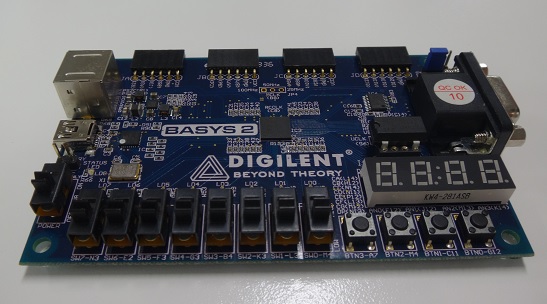

FPGA (というか VHDL) で遊ぶために BASYS2 という教育ボードを手に入れたので、そのセットアップと、主要ツールの使い方についてメモ。

- インストール手順

- 環境の準備

Windows を使う場合であれば、Windows 7 の 32bit 版を用意したほうが無難なようです。(以後のバージョンや 64bit 版だと色々と問題があるとの噂…)

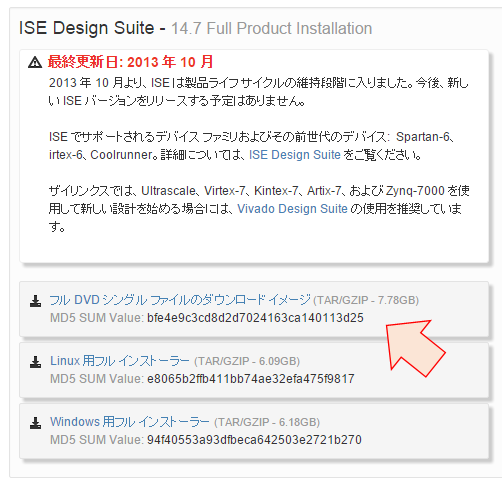

- Xilinx ISE WebPack のインストール

以下のサイトから ISE をダウンロードしセットアップします。

http://japan.xilinx.com/support/download/index.html/content/xilinx/ja/downloadNav/design-tools.html

ISE Design Suite をダウンロードし、ライセンス選択時に WebPack を選択します。Licence ファイルは別途入手します。(ユーザー登録すると貰えます)

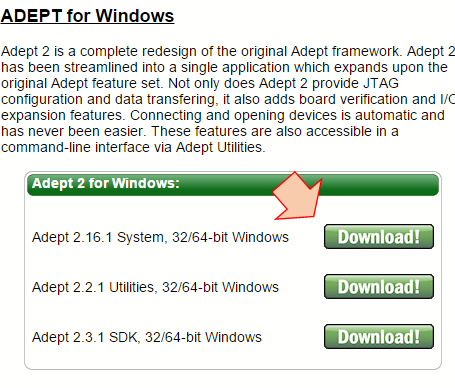

インストール自体はウィザードに従えばひっかかりはないと思いますが、インストール時間はかなりかかります。また、インストールに必要なディスク容量が 15GB 程度必要なので注意します。 - Degilent ADEPT のインストール

以下のサイトから、Adept 2.16.1 System をダウンロードしてインストールします。

http://www.digilentinc.com/Products/Detail.cfm?NavPath=2,66,828&Prod=ADEPT2

また、ついでに Adept 2.2.1 Utilities もダウンロードしてインストールします。(使わないかもしれませんが念のため)

- 環境の準備

- プロジェクトの作成とダウンロード

主に http://junkbox.wicurio.com/index.php?VHDL%E3%81%8B%E3%82%89%E4%BD%9C%E6%88%90 を参考にしました。

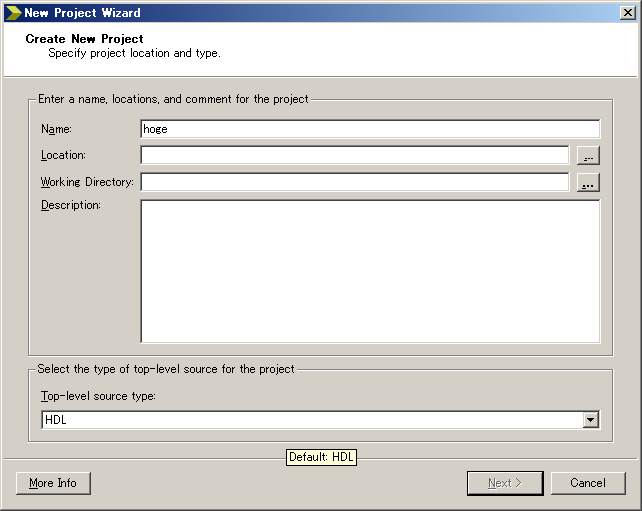

以下で不足する情報は、上記リンクを確認してみてください。- まず ISE を起動して、File -> New Project でプロジェクトを作ります。Name は適当に。Top Level Source Type は "HDL" で。Location はプロジェクトの保存場所なので任意のフォルダを設定します。

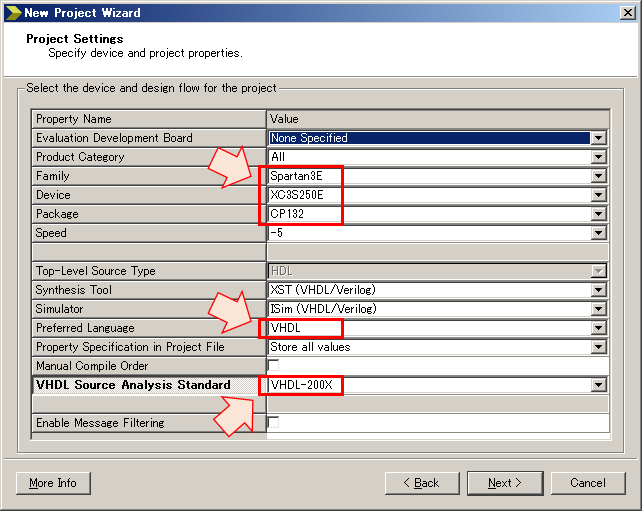

- Family を "Spartan 3E", Device を "XC3S250E", Package を "CP132" に設定。あと、VHDL Source Analysus Standard を "VHDL-200X" とします。

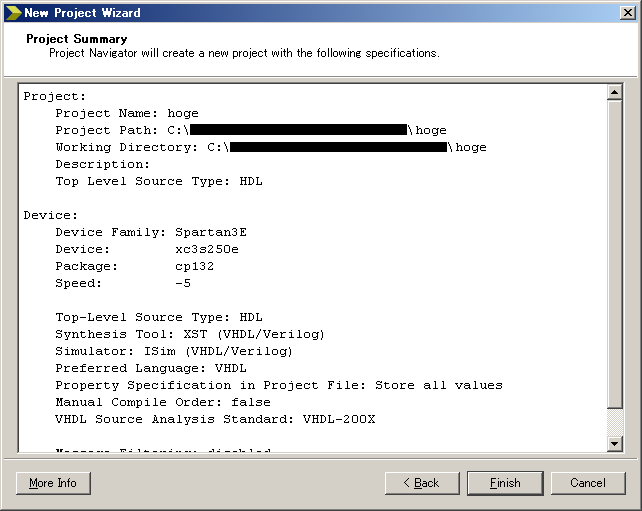

- "Finish" で。

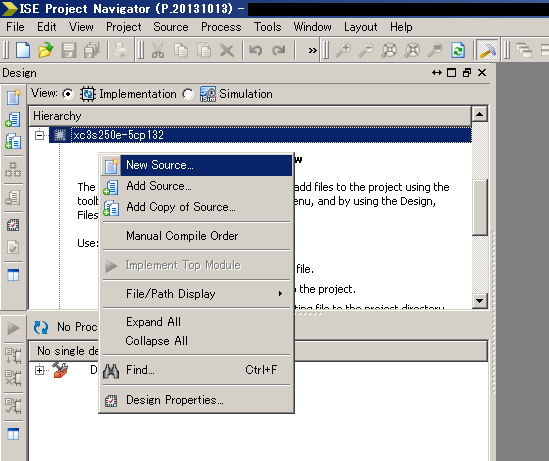

- "xc3s250e-5cp 132" を右クリックして "New Source" を選択。

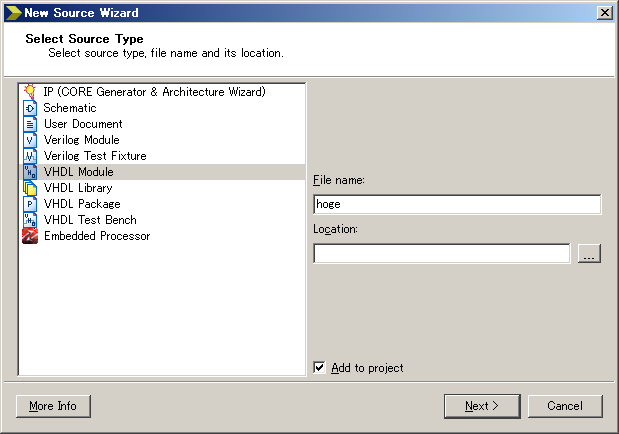

- VHDL モジュールを選択。ファイル名は適当に。

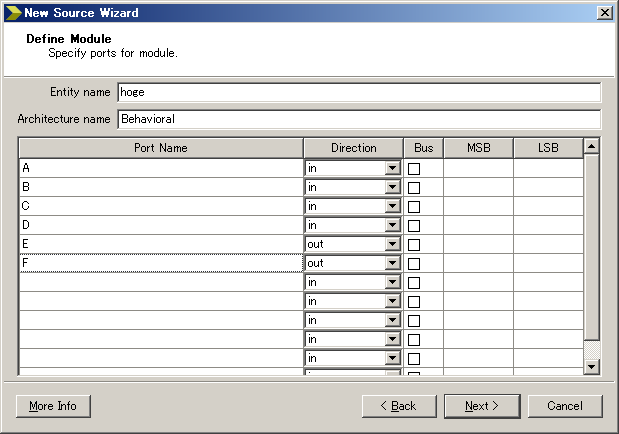

- 入出力ポートを設定します。今回は A~D を in, E~F をout に設定。(A~F は変数名なので任意でよい)

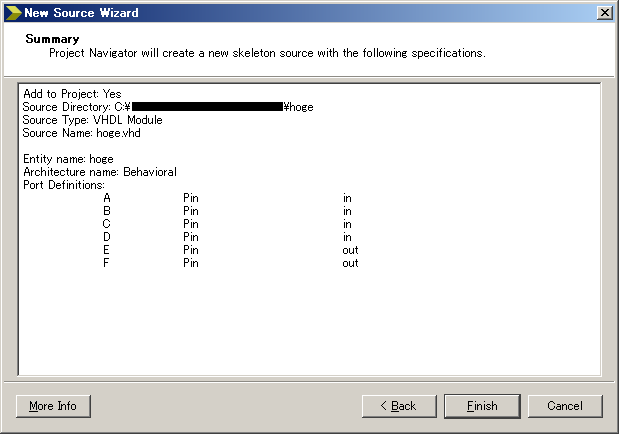

- "Finish" で。

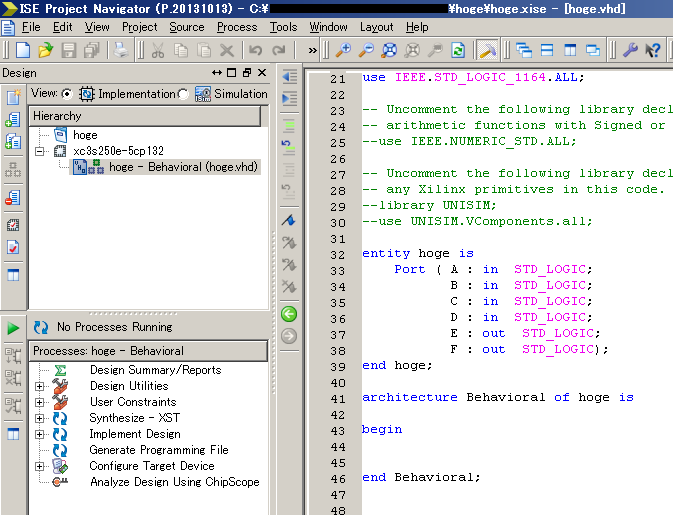

- すると、ソースコードエディタに展開します。上記で設定したポート設定がコードに反映されています。

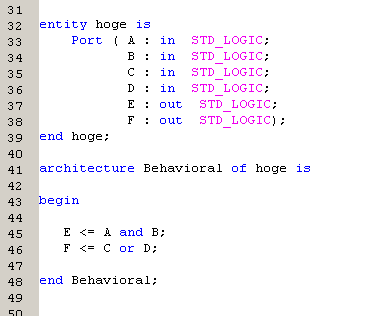

- hello world っぽいコードを書きます。(begin と end の間)

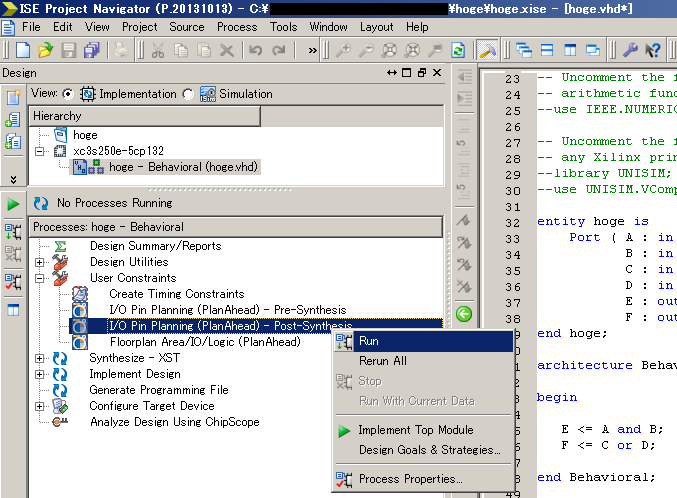

- "User Constraints" の "I/O pin planning (PlanAhead) - Post-Synthesis" を右クリックし、"Run" を選択します。

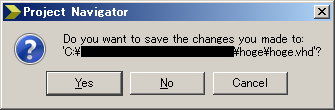

- "Yes" で。(hoge.vhd を保存します)

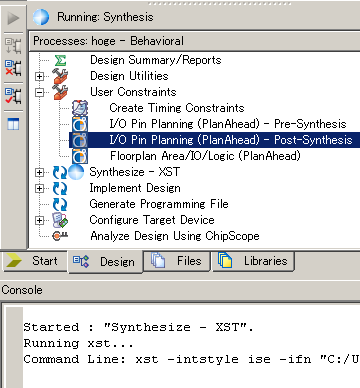

- Plan Ahead の起動が開始されます。

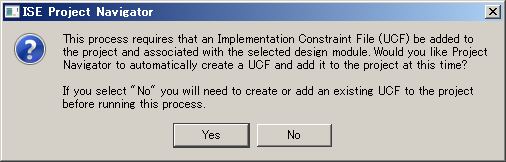

- "YES" で。(.ucf ファイルを作ります)

- Plan Ahead が起動していないように感じたら、タスクマネージャーで確認します。多分起動しているので我慢強く待ちます(汗

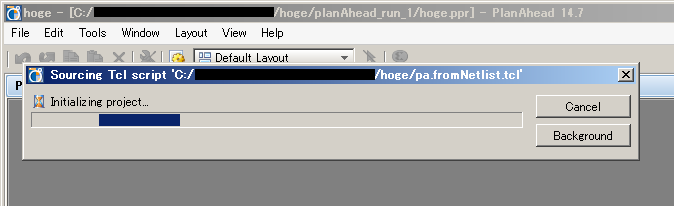

- Plan Ahead 起動中です。

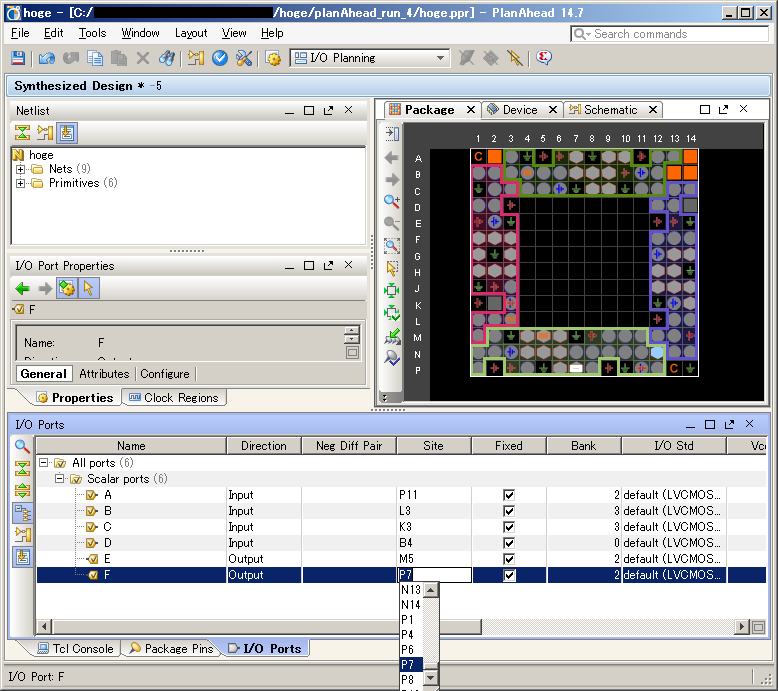

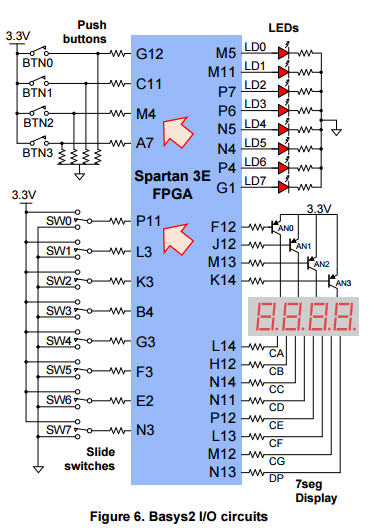

- ポートの割り付けをします。site に指定する名称はボードのシルク印刷に記されています。

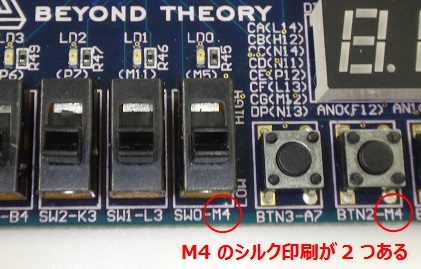

- ところが私の BASYS2 はなぜか M4 の印刷が複数あり、タクトスイッチのほうはシルク印刷通り M4 ですが、スライドスイッチのほうは M4 ではなく P11 なので注意します。

本来のピンアサイン [リファレンスマニュアル] [リンク元のページ]

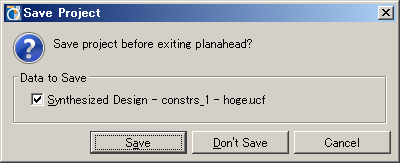

- Plan Ahead を閉じます。以下のダイアログが表示されたら "Save" で。

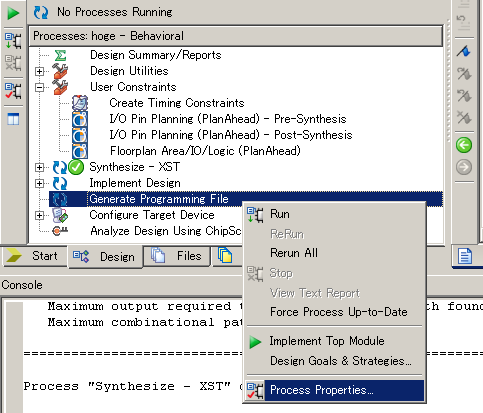

- ISE に戻り、"Genarate Program File" を右クリックし、"Process Properties" を選択します。

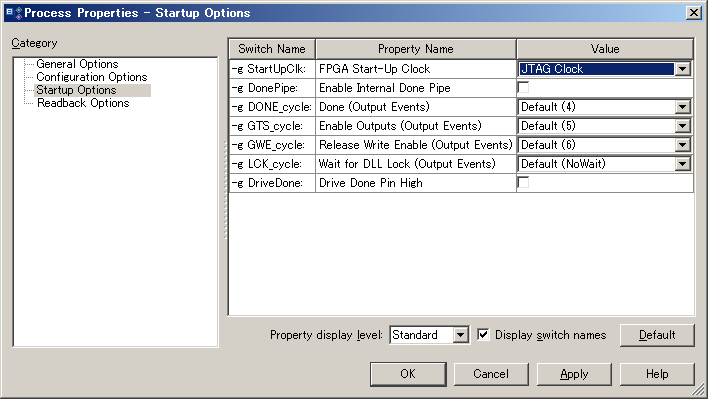

- "FPGA Start-Up Clock" を "JTAG Clock" に変更し、"OK" を押します。

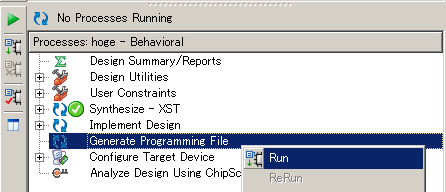

- "Genarate Program File" を右クリックし、"Run" を選択します。

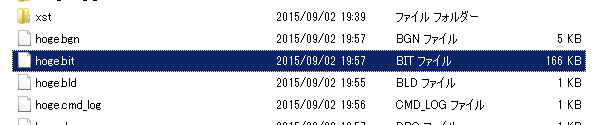

- エラーがなければ、プロジェクトのフォルダに .bit ファイルが作成されています。

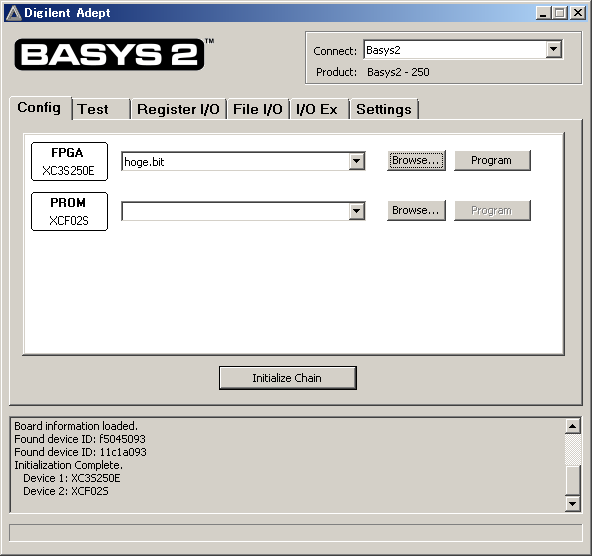

- Digilint Adept を起動。この .bit ファイルを 選択しダウンロードします。

- まず ISE を起動して、File -> New Project でプロジェクトを作ります。Name は適当に。Top Level Source Type は "HDL" で。Location はプロジェクトの保存場所なので任意のフォルダを設定します。

oh

始めまして。

超初心者の私でもFPGAを操作できることができ、大変うれしかったです。

本WEBは貴重です。次のステップもあると参考にしたいと思います。

Link | 2016年4月29日 23:34